# Digitaltechnik Vorlesung 2: Zusätzliches Material

Mathieu Luisier

Institut für Integrierte Systeme, ETH Zürich

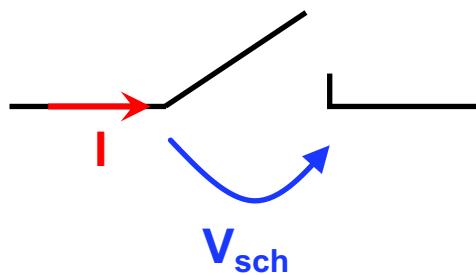

# Schalter: Strom und Spannung

Wann fliesst ein Strom  $I$  durch einen Schalter?

Kann eine Spannung  $V_{sch}$  über einem Schalter gemessen werden?

Offener Schalter

Ersatz

$$I = 0$$

$$|V_{sch}| \geq 0$$

Kein Strom,

Spannung möglich

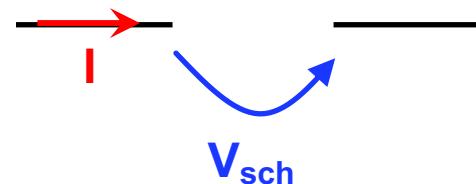

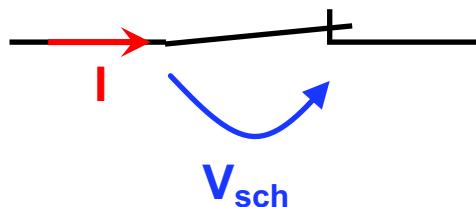

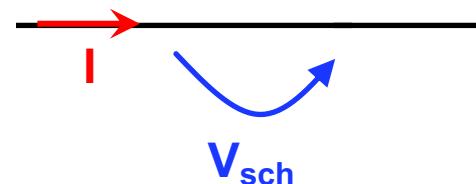

Geschlossener Schalter

Ersatz

$$|I| \geq 0$$

$$V_{sch} = 0$$

Strom möglich,

keine Spannung

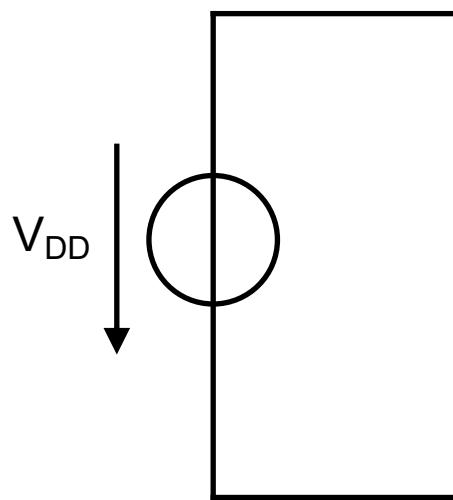

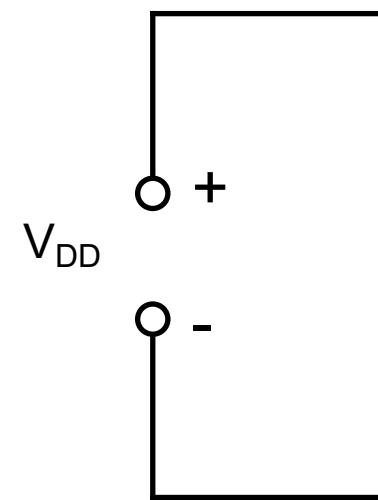

# Spannungsquelle

Definition der Spannungsquelle: beide Darstellungen sind äquivalent

≡

Stromrichtung

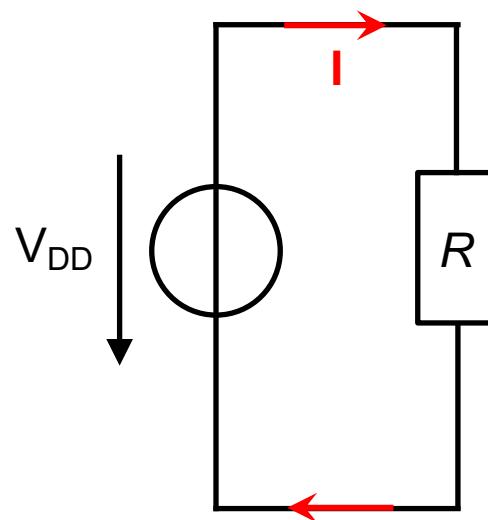

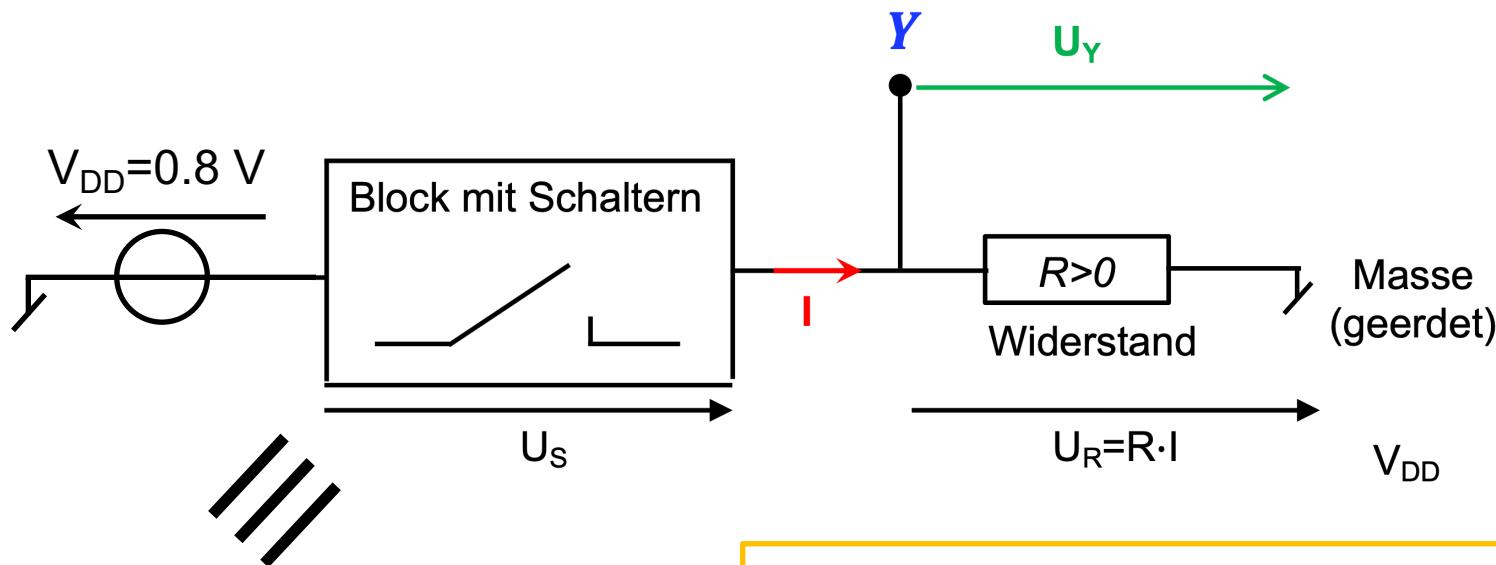

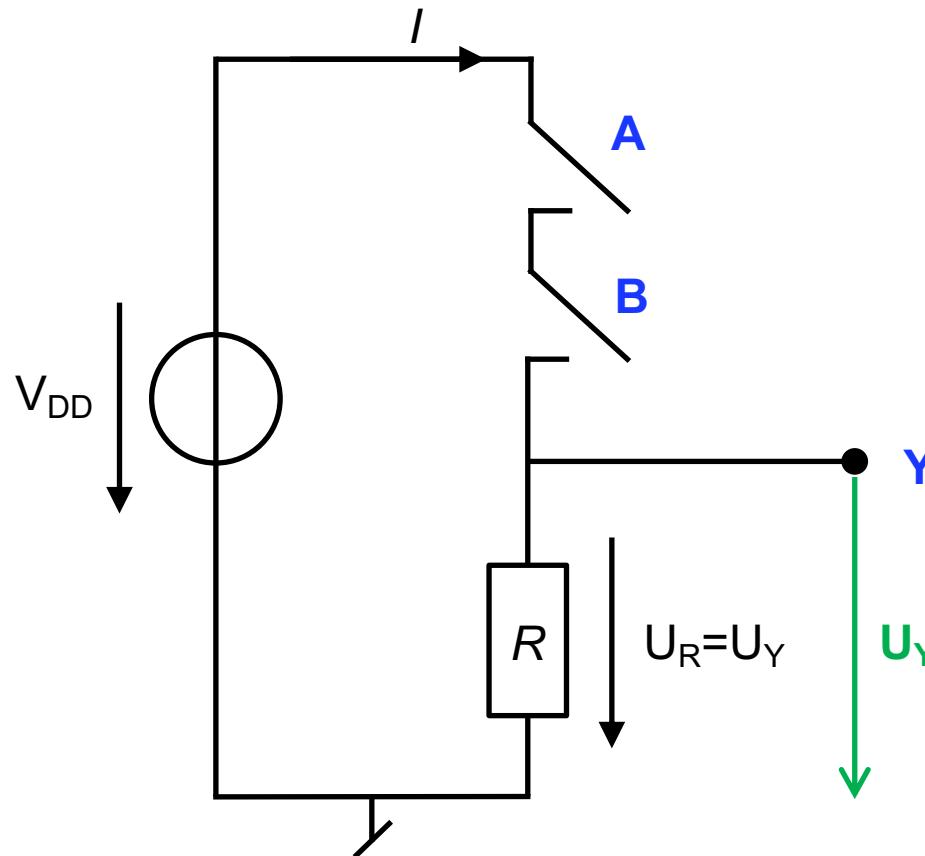

# Analyse von Schaltungen in der Schalterlogik

Diese beiden Schaltungen sind äquivalent:

$U_S$ : Spannung über dem Schalterblock

$U_R$ : Spannung über dem Widerstand  $R$

$U_Y$ : Ausgangsspannung

## Analyse:

$$V_{DD} = U_S + U_R \text{ und } U_Y = U_R$$

1. Wenn es keinen Strompfad gibt ( $I=0$ ):

$U_R=0, U_S=V_{DD} \Rightarrow U_Y=0$  (logische 0)

2. Wenn es einen Strompfad gibt ( $I \neq 0$ ):

$U_R=V_{DD}, U_S=0 \Rightarrow U_Y=V_{DD}$  (logische 1)

# UND Verknüpfung

Alternative Form der Schaltung für die UND-Verknüpfung

Diese Schaltung und die auf Slide 12 des Vorlesung2.pdf Dokuments sind identisch. Sie sind nur anders gezeichnet

# ODER Verknüpfung

Wenn Aussage **A** (Eingang) wahr **oder** Aussage **B** (Eingang) wahr ist, dann ist Aussage **Y** (Ausgang) wahr

## (1) Wahrheitstabelle:

| A | B | Y |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

$0 \hat{=} 0 \text{ V (Masse)}$

$1 \hat{=} 0.8 \text{ V (V}_{\text{DD}}\text{)}$

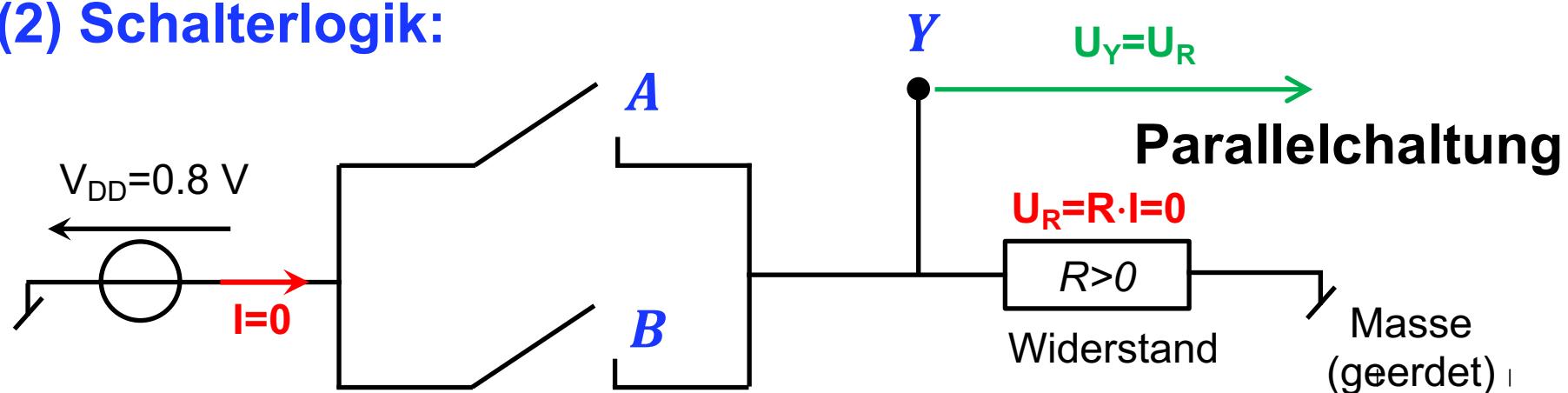

## (2) Schalterlogik:

# ODER Verknüpfung

Wenn Aussage **A** (Eingang) wahr **oder** Aussage **B** (Eingang) wahr ist, dann ist Aussage **Y** (Ausgang) wahr

## (1) Wahrheitstabelle:

| A | B | Y |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

$0 \hat{=} 0 \text{ V (Masse)}$

$1 \hat{=} 0.8 \text{ V (V}_{\text{DD}}\text{)}$

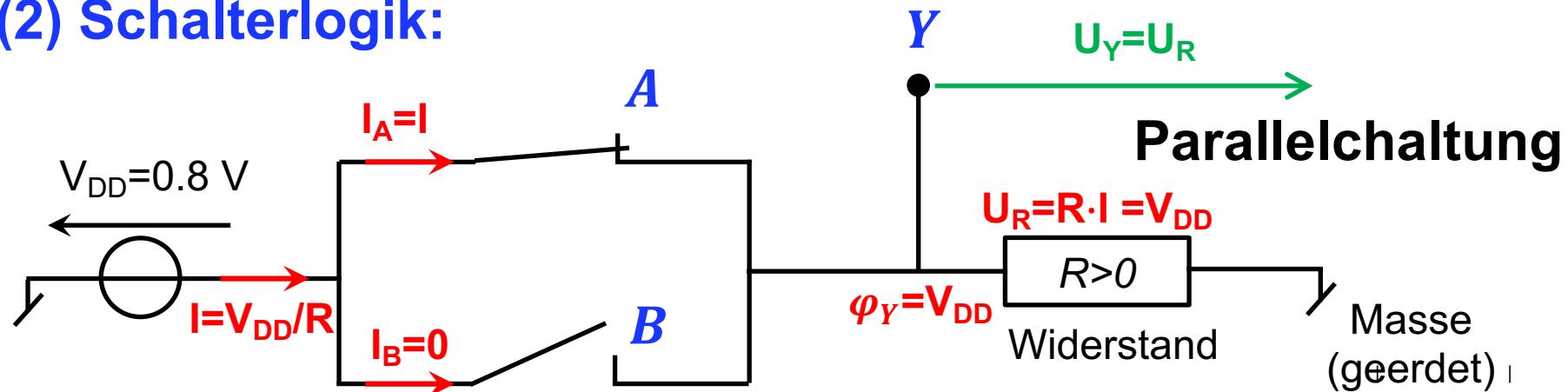

## (2) Schalterlogik:

# ODER Verknüpfung

Wenn Aussage **A** (Eingang) wahr **oder** Aussage **B** (Eingang) wahr ist, dann ist Aussage **Y** (Ausgang) wahr

## (1) Wahrheitstabelle:

| A | B | Y |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

$0 \hat{=} 0 \text{ V (Masse)}$

$1 \hat{=} 0.8 \text{ V (V}_{\text{DD}}\text{)}$

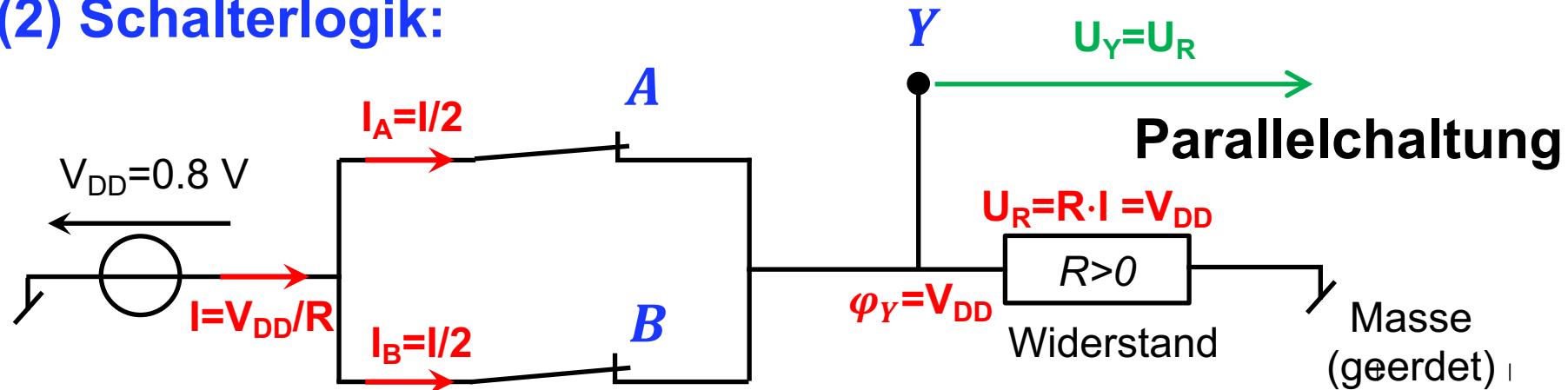

## (2) Schalterlogik:

# ODER Verknüpfung

Wenn Aussage **A** (Eingang) wahr **oder** Aussage **B** (Eingang) wahr ist, dann ist Aussage **Y** (Ausgang) wahr

## (1) Wahrheitstabelle:

| A | B | Y |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

$0 \hat{=} 0 \text{ V (Masse)}$

$1 \hat{=} 0.8 \text{ V (V}_{\text{DD}}\text{)}$

## (2) Schalterlogik:

# ÄQUIVALENZ-Verknüpfung, XNOR-GATTER

## Wahrheitstabelle:

| <b>A</b> | <b>B</b> | $S = \bar{A} \wedge \bar{B}$ | $Q = A \wedge B$ | $Y = S \vee Q$ |

|----------|----------|------------------------------|------------------|----------------|

| 0        | 0        | 1                            | 0                | 1              |

| 0        | 1        | 0                            | 0                | 0              |

| 1        | 0        | 0                            | 0                | 0              |

| 1        | 1        | 0                            | 1                | 1              |

Nur wenn beide Eingänge äquivalent sind, ist der Ausgang 1

# Wahrheitstabelle eines UND-Gatters mit 3 Eingängen

Die Wahrheitstabelle eines UND-Gatters mit 3 Eingängen

besitzt **4** Spalten und  $2^3=8$  Zeilen

| A | B | C | Y |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 1 |

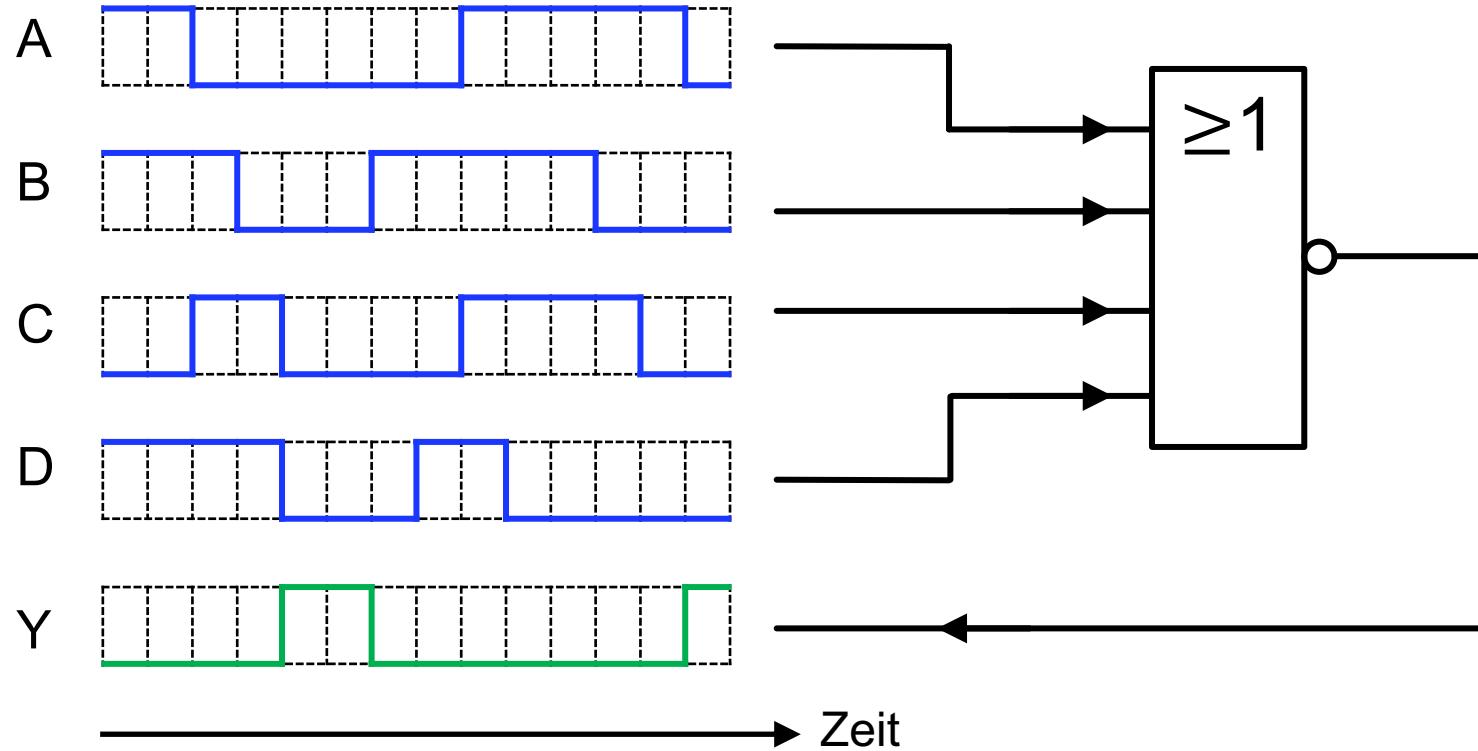

# NOR-Gatter mit 4 Eingängen

Nur wenn  $A=B=C=D=0$  ist  $Y=1$

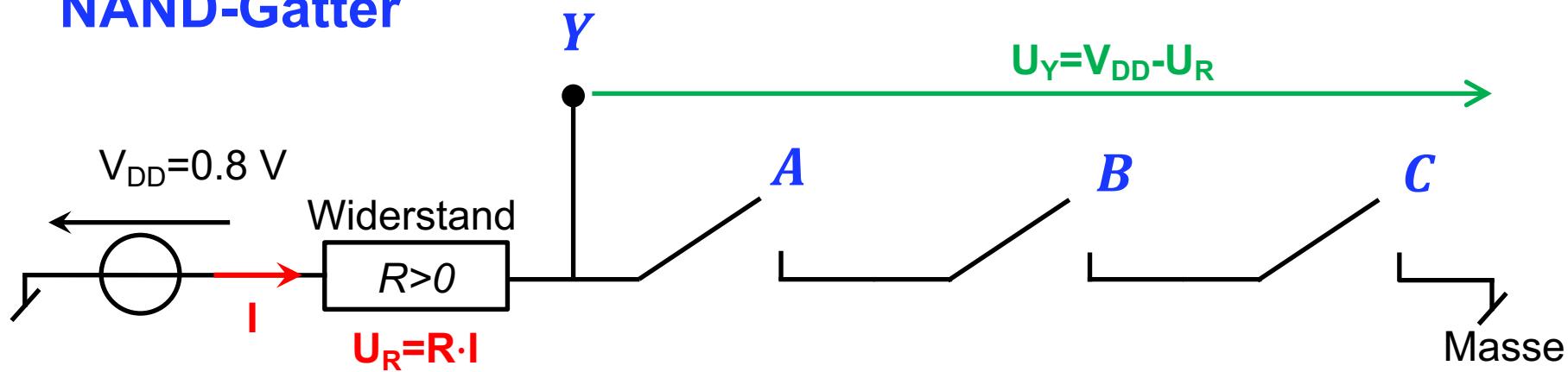

# NAND mit 3 Eingängen aus 3 Schaltern

## NAND-Gatter

Wenn  $A=B=C=1$ , dann ist der Ausgang  $Y$  mit der Masse gebunden, i.e.  $Y=1$  und die angelegte Spannung  $V_{DD}=0.8 \text{ V}$  fällt über den Serie Widerstand  $R$ .

Der Vorteil dieser Variante ist, dass die Verzögerungszeit, bis das Signal am Ausgang  $Y$  geändert wird, wenn die Eingänge modifiziert werden, viel kleiner ist als im Fall von kombinierten Grundgattern.

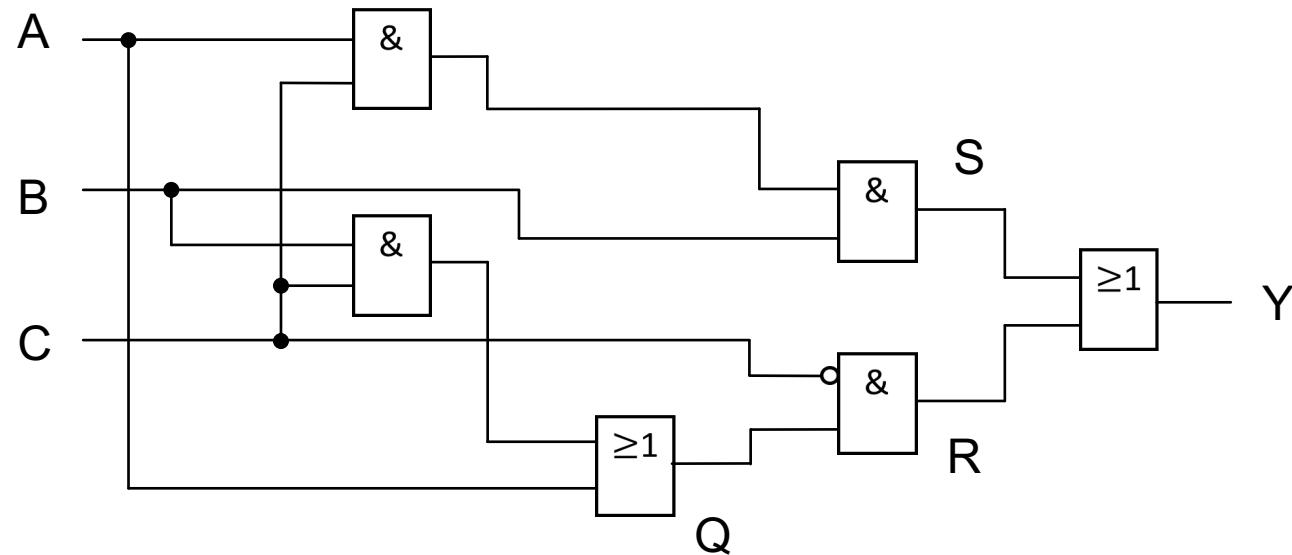

# Schaltnetz zu analysieren (1)

## Schaltnezt

## Logische Gleichung

$$Y = ((A \wedge C) \wedge B) \vee (((B \wedge C) \vee A) \wedge \bar{C})$$

# Schaltnetz zu analysieren (2)

## Wahrheitstabelle

| A | B | C | S | Q | R | Y |

|---|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 | 0 | 0 | 0 |

| 0 | 1 | 0 | 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 | 1 | 0 | 0 |

| 1 | 0 | 0 | 0 | 1 | 1 | 1 |

| 1 | 0 | 1 | 0 | 1 | 0 | 0 |

| 1 | 1 | 0 | 0 | 1 | 1 | 1 |

| 1 | 1 | 1 | 1 | 1 | 0 | 1 |

$$S = (A \wedge C) \wedge B \quad Q = (B \wedge C) \vee A \quad R = Q \wedge \bar{C} \quad Y = S \vee R$$

# Wann ist $Y=1$ ?

**Es gibt 3 Fälle, wo  $Y=1$ :**

- Wenn A=1 UND B=0 UND C=0 **(1)**

## ODER

- Wenn A=1 UND B=1 UND C=0 **(2)**

## ODER

- Wenn A=1 UND B=1 UND C=1 **(3)**

Diese 3 Bedingungen können so zusammengefasst werden:

$$Y = (A \wedge \overline{B} \wedge \overline{C}) \vee (A \wedge B \wedge \overline{C}) \vee (A \wedge B \wedge C)$$

**(1)**                    **(2)**                    **(3)**