# Digitaltechnik Vorlesung 2: Logische Verknüpfungen

Mathieu Luisier

Institut für Integrierte Systeme, ETH Zürich

# Übungsräume und Hilfsassistenten

Die erste **Übungsstunde** findet an diesem Donnerstag um 14:15 statt

| Gruppe            | Hilfsassistent(in)     | Raum      |

|-------------------|------------------------|-----------|

| Gruppe 1: A - Be  | Laura Franziska Heintz | ETZ E8    |

| Gruppe 2: Bi - Di | Selina Poo             | ETZ E9    |

| Gruppe 3: Dj - Ge | Jan Limacher           | ETZ F91   |

| Gruppe 4: Gö - I  | Yunfei Li              | HG D3.1   |

| Gruppe 5: J - Li  | Lelia Ruckstuhl        | HG D5.1   |

| Gruppe 6: Lu - Na | Onno Riedel            | HG E33.5  |

| Gruppe 7: Ne - Q  | Deniz Utku Akbaş       | HG G26.3  |

| Gruppe 8: R - Se  | Timo Rüeger            | ETZ J91   |

| Gruppe 9: Sh - U  | Veronika Möller        | ETZ E6    |

| Gruppe 10: V - Z  | Finn Crohn             | GLC E29.2 |

<https://moodle-app2.let.ethz.ch/mod/page/view.php?id=1232570>

## Motivation:

Vorstellung von elementaren Basisfunktionen der Digitaltechnik, die mehrere Eingänge in einen Ausgang umwandeln. Solche Funktionen sind für das Arbeiten mit binären/digitalen Systemen erforderlich und werden heute vorgestellt.

## Lernziele:

- Logische Grundfunktionen kennenlernen sowie ihre Funktionalität und ihre Darstellung

- Aufbau komplexer Funktionen aus zusammengesetzten Grundgattern (**UND**, **ODER**, **NICHT**)

- Analyse komplexer Gatter, wo die Funktionen eines aus den Grundgattern zusammengesetzten Schaltwerks bestimmt werden muss.

# Was werden wir in dieser Vorlesung studieren?

Integrierte Schaltung

Vorlesung 5

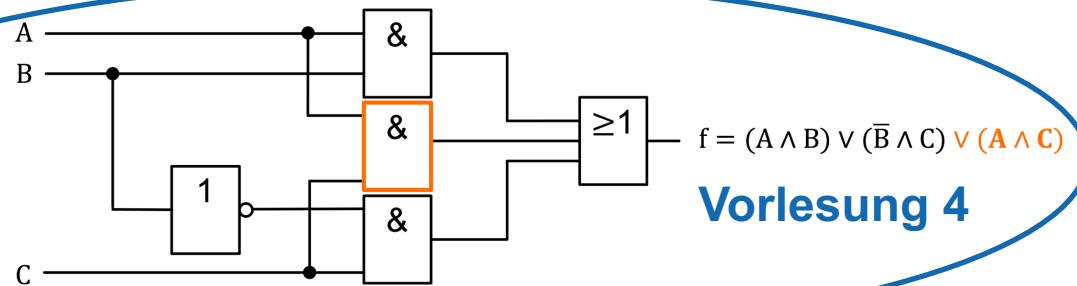

Vorlesung 4

Basisschaltungen

NOT

AND

Vorlesung 2

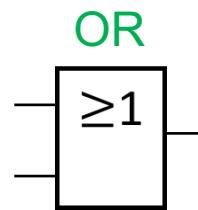

OR

XOR

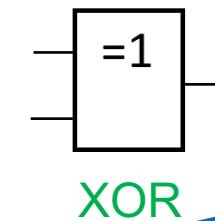

Vorlesung 3

P-Typ

N-Typ

Transistoren

Grundblöcke

Logische Bauelemente

Wie kombinieren wir

diese Komponenten?

- Basisfunktionen

- Nützliche Konzepte

- UND, ODER, NICHT Verknüpfungen

- Schaltnetzaanalyse

- Zusammengesetzte Gatter

- Schaltungen aus Grundgattern

- Zusammenfassung

Reichardt Kapitel 3

- **Basisfunktionen**

- Nützliche Konzepte**

- UND, ODER, NICHT Verknüpfungen**

- **Schaltnetzaanalyse**

- Zusammengesetzte Gatter**

- Schaltungen aus Grundgattern**

- **Zusammenfassung**

# Schaltfunktionen

Eine Schaltfunktion  $f$  nimmt mehrere Variablen  $X_i$ , z.B.  $N$ , als Eingang und produziert eine einzige Variable  $Y$  als Ausgang:

$$Y = f(X_0, X_1, X_2, \dots, X_{N-1})$$

wobei der Informationsgehalt der Variablen 1 Bit (Binary Digit), i.e.  $X_i, Y \in \{0, 1\}$ , beträgt

Jede Variable  $X_i$  kann durch einen Schalter dargestellt werden:

$$X_i = 0$$

Schalter auf (kein Strom)

$$X_i = 1$$

Schalter zu (Strom)

Die Schaltfunktion  $f$  kann durch eine Kombination von Schaltern repräsentiert werden. Das Ergebnis ist  $1$ , wenn die am Ausgang  $Y$  gemessene Spannung,  $U_Y$ , der Speisespannung entspricht.

# Wahrheitstabellen

Schaltfunktionen lassen sich in Form einer **Wahrheitstabelle** („truth table“) darstellen.

In Wahrheitstabellen werden auf der linken Seite alle möglichen Wertekombinationen der Eingänge aufgelistet. Auf der rechten Seite befindet sich das Ergebnis für die Ausgangsvariable.

Die Wahrheitstabelle einer Schaltfunktion  $f$  mit  $N$  Eingängen enthält deshalb  $N + 1$  Spalten und  $2^N$  Reihen.

In der Regel werden die Zeilen der Wahrheitstabelle so angeordnet, dass sie aufsteigenden Binärzahlen entsprechen.

Wahrheitstabellen sind **zentrale Elemente** der Digitaltechnik Vorlesung. Sie werden immer wieder vorkommen.

# Wahrheitstabellen

Beispiel:  $Y = f(A, B, C)$  (Schaltfunktion mit  $N=3$  Eingängen)

| A | B | C | Y                      |

|---|---|---|------------------------|

| 0 | 0 | 0 | $f(0,0,0) \in \{0,1\}$ |

| 0 | 0 | 1 | $f(0,0,1) \in \{0,1\}$ |

| 0 | 1 | 0 | $f(0,1,0) \in \{0,1\}$ |

| 0 | 1 | 1 | $f(0,1,1) \in \{0,1\}$ |

| 1 | 0 | 0 | $f(1,0,0) \in \{0,1\}$ |

| 1 | 0 | 1 | $f(1,0,1) \in \{0,1\}$ |

| 1 | 1 | 0 | $f(1,1,0) \in \{0,1\}$ |

| 1 | 1 | 1 | $f(1,1,1) \in \{0,1\}$ |

2<sup>3</sup>=8 Zeilen

Eingänge (3 Spalten)      Ausgang

- **Basisfunktionen**

Nützliche Konzepte

**UND, ODER, NICHT Verknüpfungen**

- Schaltnetzaanalyse

Zusammengesetzte Gatter

Schaltungen aus Grundgattern

- Zusammenfassung

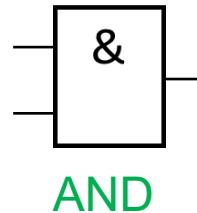

# UND Verknüpfung (1)

Wenn Aussage **A** (Eingang) wahr **und** Aussage **B** (Eingang) wahr sind, dann ist Aussage **Y** (Ausgang) wahr

**Annahme:** wahr (true) = logischer Zustand 1, falsch (false) = logischer Zustand 0

## (1) Wahrheitstabelle:

| A | B | Y |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

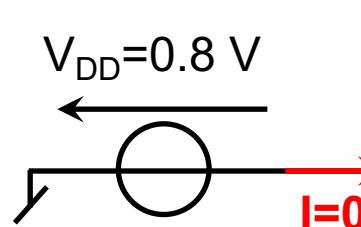

$$\begin{aligned}0 &\hat{=} 0 \text{ V (Masse)} \\1 &\hat{=} 0.8 \text{ V (V}_{\text{DD}})\end{aligned}$$

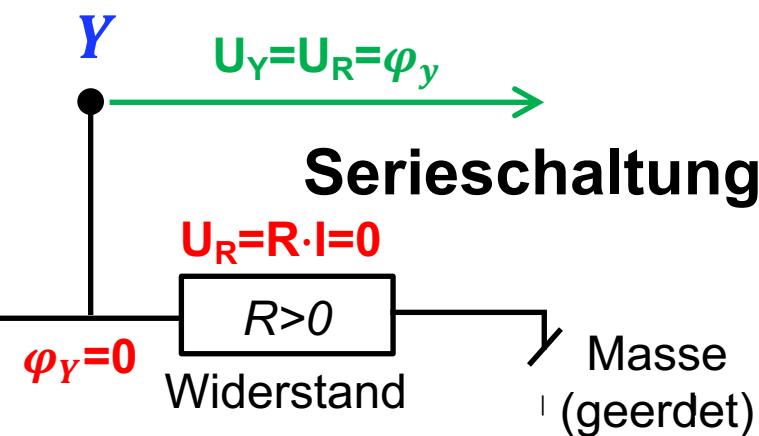

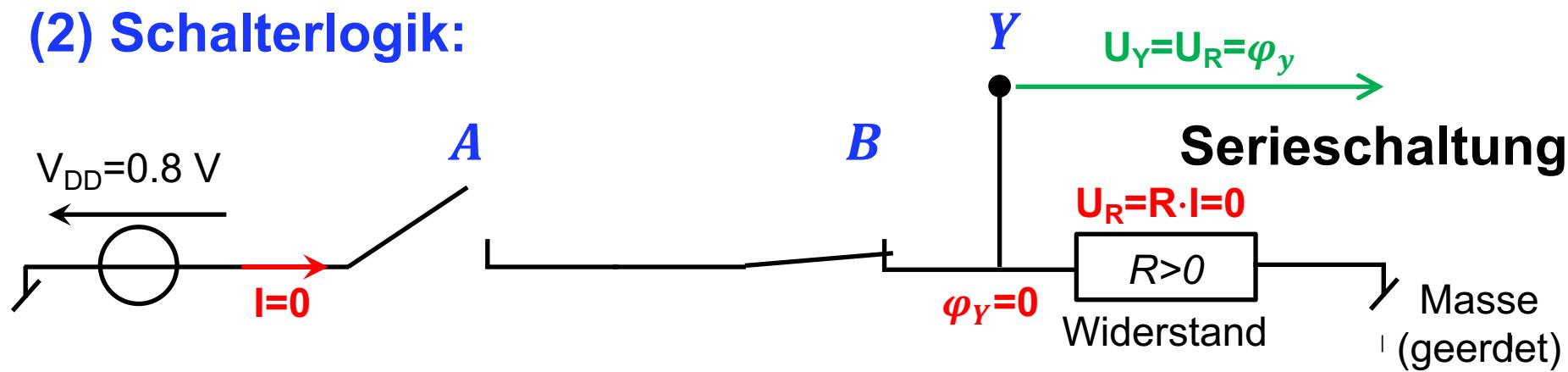

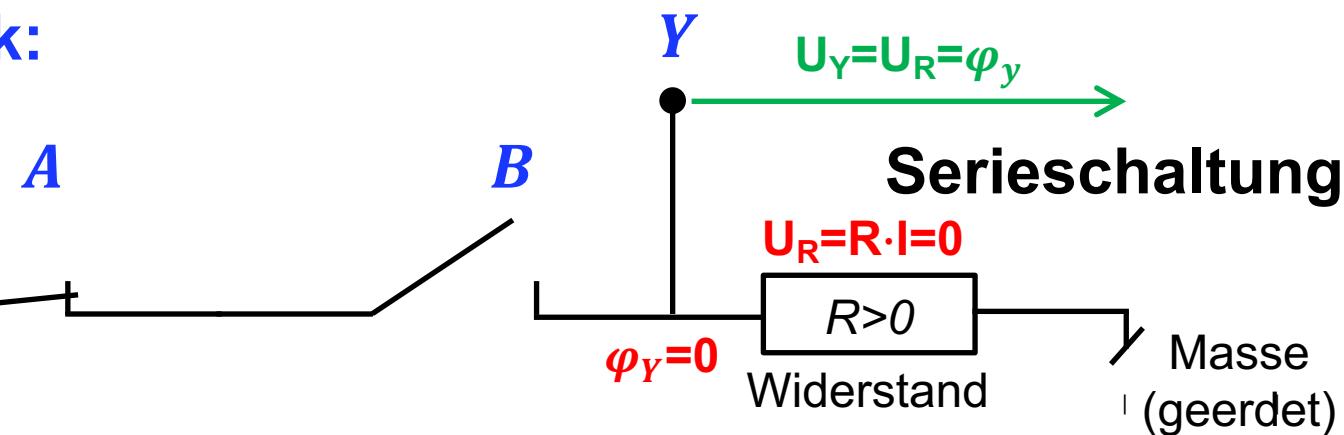

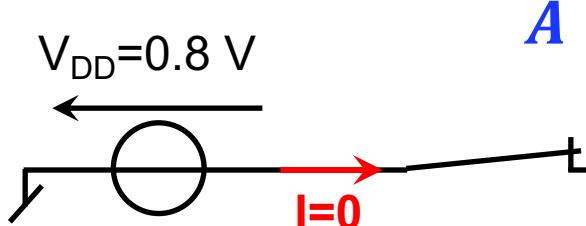

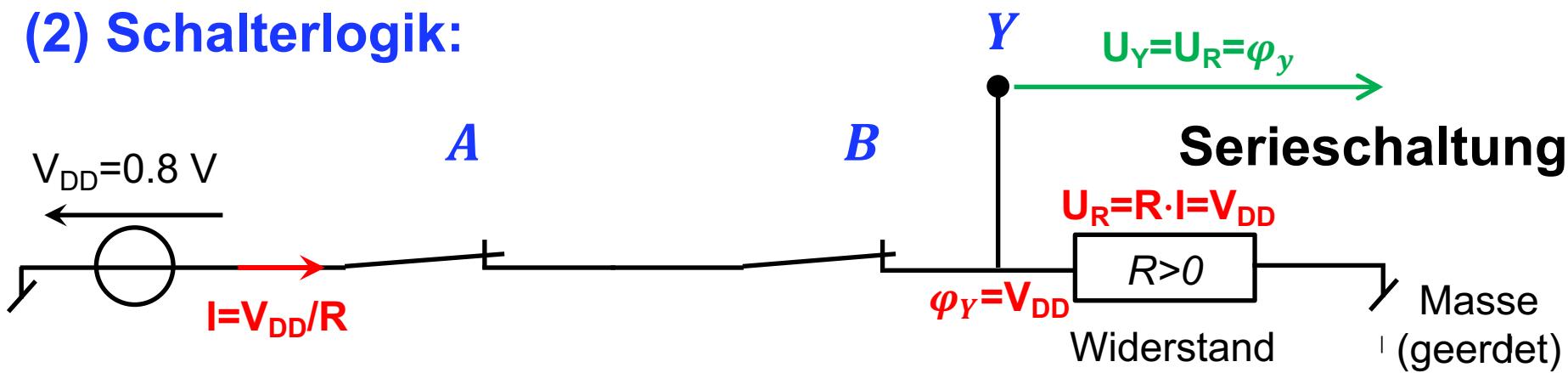

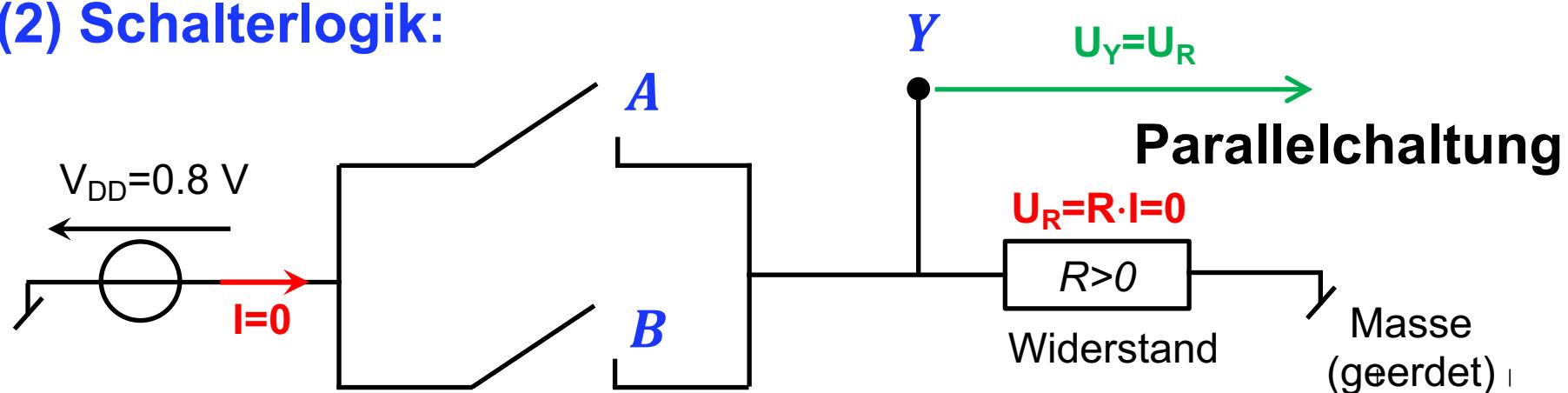

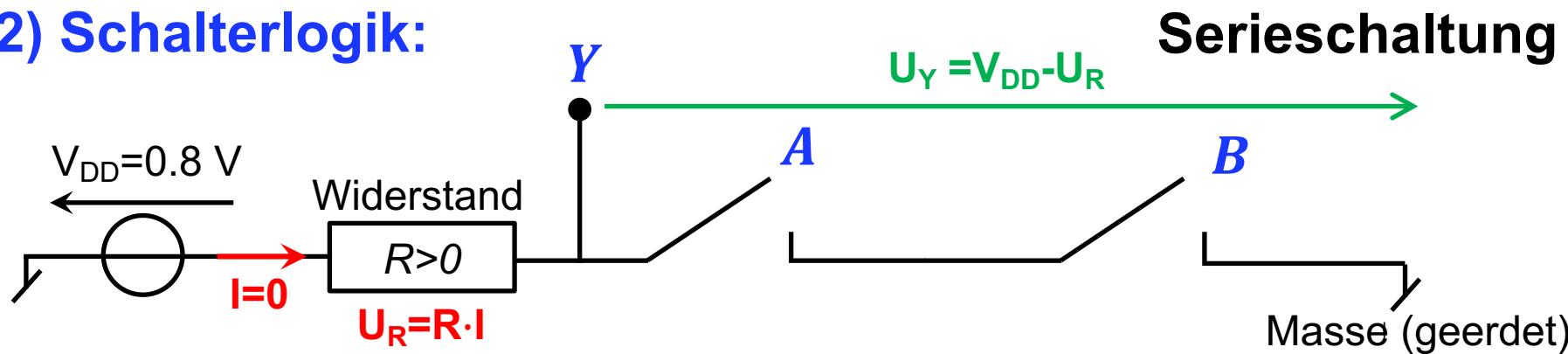

## (2) Schalterlogik:

**A**

**B**

# UND Verknüpfung (1)

# UND Verknüpfung (1)

Wenn Aussage **A** (Eingang) wahr **und** Aussage **B** (Eingang) wahr sind, dann ist Aussage **Y** (Ausgang) wahr

**Annahme:** wahr (true) = logischer Zustand 1, falsch (false) = logischer Zustand 0

## (1) Wahrheitstabelle:

| A | B | Y |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

$$\begin{aligned}0 &\hat{=} 0 \text{ V (Masse)} \\1 &\hat{=} 0.8 \text{ V (V}_{\text{DD}})\end{aligned}$$

## (2) Schalterlogik:

# UND Verknüpfung (1)

Wenn Aussage **A** (Eingang) wahr **und** Aussage **B** (Eingang) wahr sind, dann ist Aussage **Y** (Ausgang) wahr

**Annahme:** wahr (true) = logischer Zustand 1, falsch (false) = logischer Zustand 0

## (1) Wahrheitstabelle:

| A | B | Y |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

$0 \hat{=} 0 \text{ V (Masse)}$

$1 \hat{=} 0.8 \text{ V (V}_{\text{DD}}\text{)}$

## (2) Schalterlogik:

# UND Verknüpfung (1)

Wenn Aussage **A** (Eingang) wahr **und** Aussage **B** (Eingang) wahr sind, dann ist Aussage **Y** (Ausgang) wahr

**Annahme:** wahr (true) = logischer Zustand 1, falsch (false) = logischer Zustand 0

## (1) Wahrheitstabelle:

| A | B | Y |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

$$\begin{aligned}0 &\hat{=} 0 \text{ V (Masse)} \\1 &\hat{=} 0.8 \text{ V (V}_{\text{DD}})\end{aligned}$$

## (2) Schalterlogik:

# UND Verknüpfung (2)

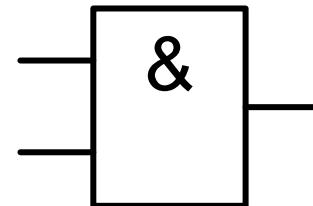

## (3) Logische Gleichung der UND (AND)-Verknüpfung:

$$Y = A \wedge B$$

$$Y = A \cdot B$$

$$Y = A * B$$

Hier verwendet

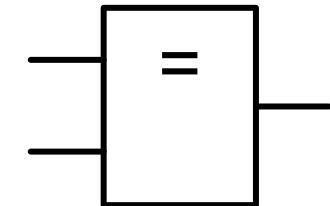

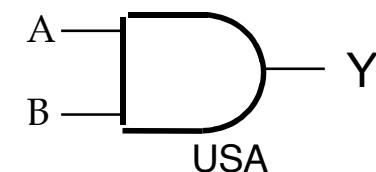

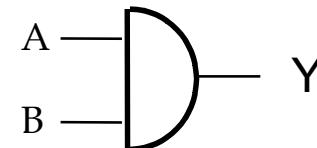

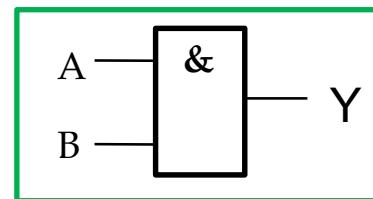

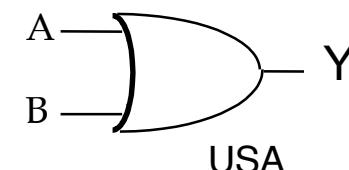

## (4) Schaltzeichen eines UND-Gatters mit 2 Eingängen:

Hier verwendet

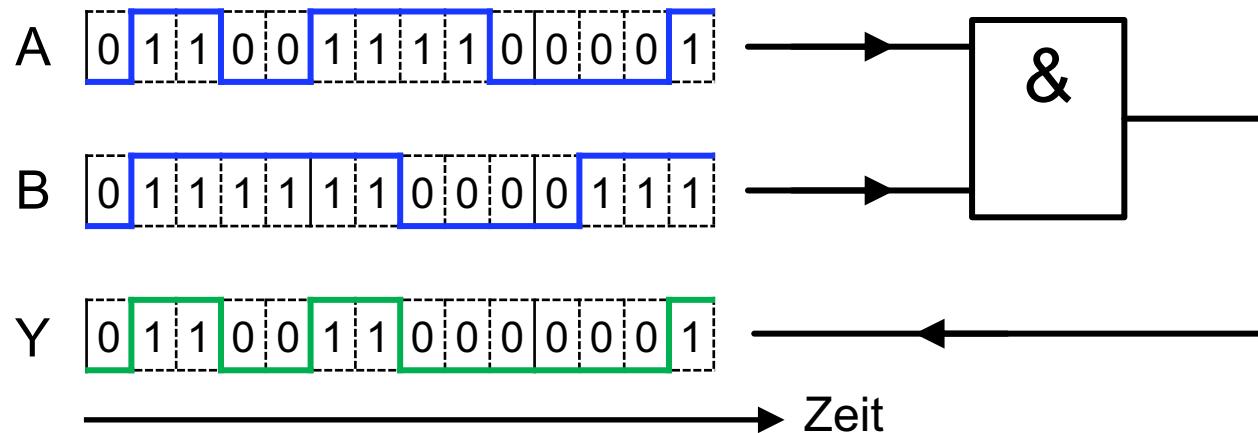

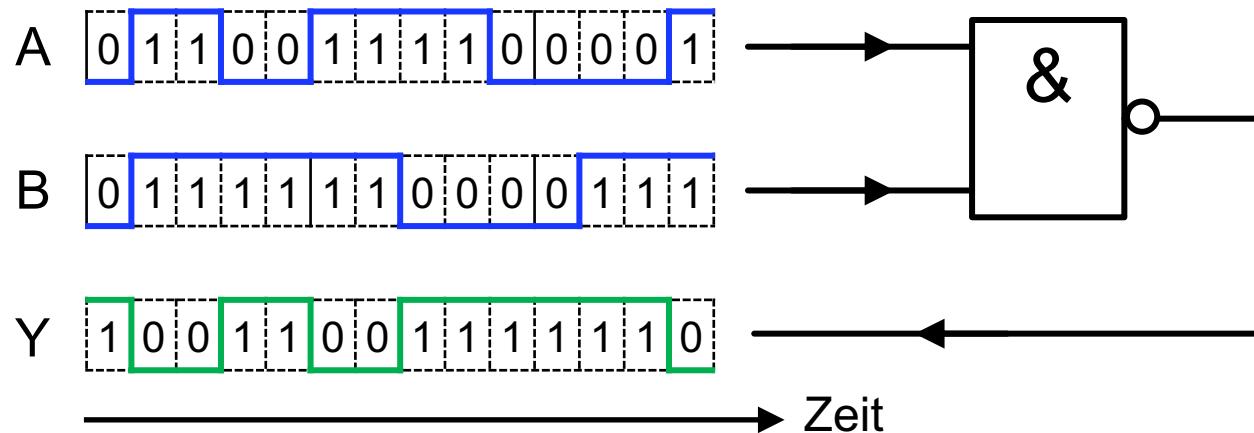

## (5) Zeitverhalten eines UND-Gatters:

# ODER Verknüpfung (1)

Wenn Aussage **A** (Eingang) wahr **oder** Aussage **B** (Eingang) wahr ist, dann ist Aussage **Y** (Ausgang) wahr

## (1) Wahrheitstabelle:

| A | B | Y |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

$0 \hat{=} 0 \text{ V}$  (Masse)

$1 \hat{=} 0.8 \text{ V}$  ( $V_{DD}$ )

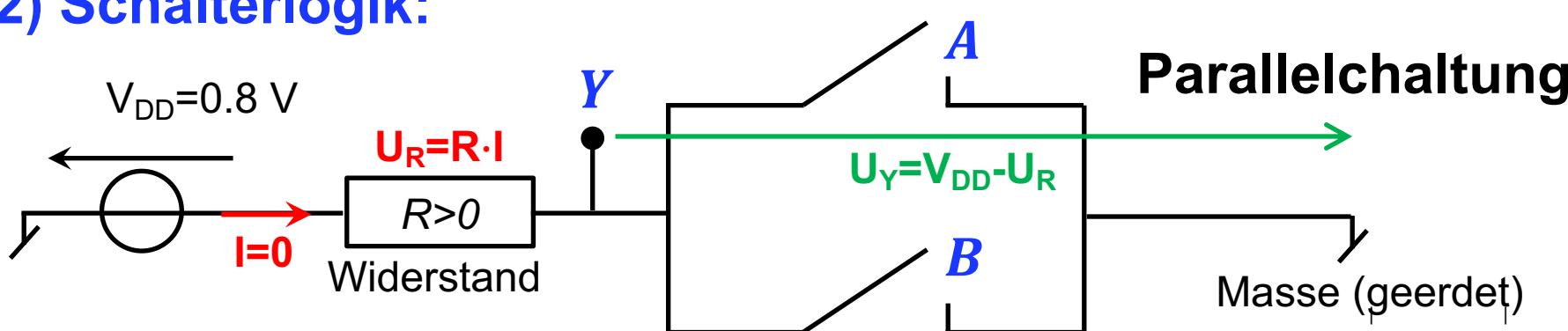

## (2) Schalterlogik:

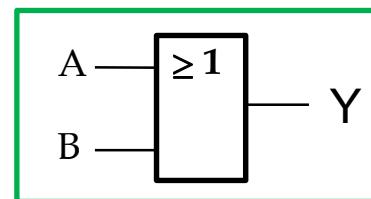

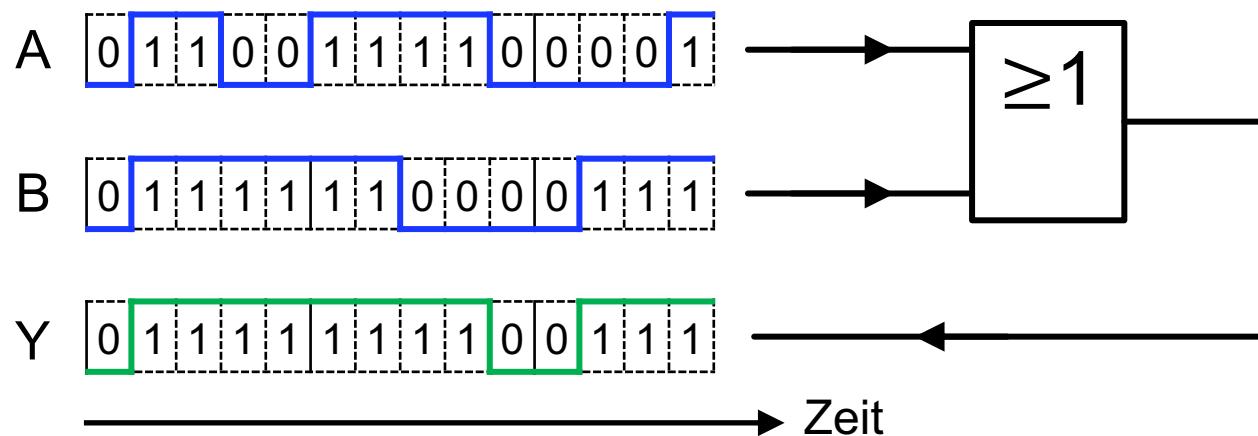

# ODER Verknüpfung (2)

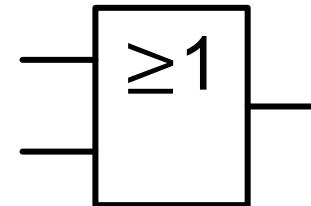

## (3) Logische Gleichung der ODER (OR)-Verknüpfung:

Hier verwendet

$$Y = A \vee B$$

$$Y = A + B$$

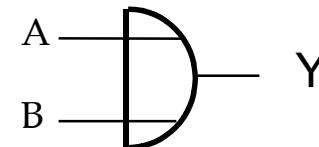

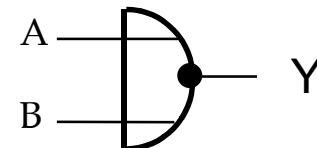

## (4) Schaltzeichen eines ODER-Gatters mit 2 Eingängen:

Hier verwendet

## (5) Zeitverhalten eines ODER-Gatters:

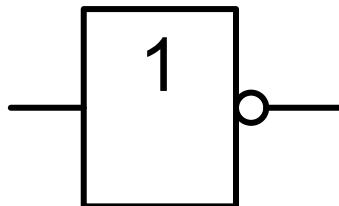

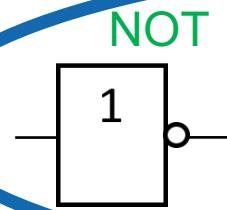

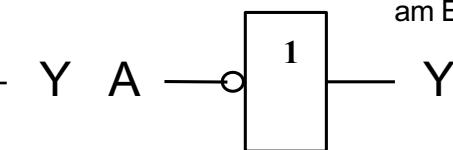

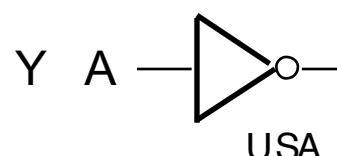

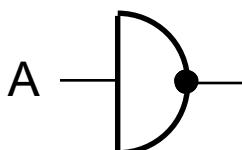

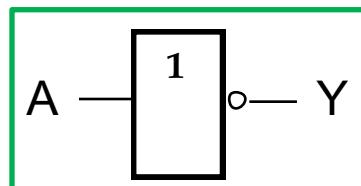

# NICHT Verknüpfung (Inverter)

Wenn Aussage **A** (Eingang) wahr ist,

dann ist Aussage **Y** (Ausgang) falsch

## (1) Wahrheitstabelle:

| A | Y |

|---|---|

| 0 | 1 |

| 1 | 0 |

## (2) Schalterlogik:

## (3) Logische Gleichung der NICHT (NOT)-Verknüpfung:

Hier verwendet

$$Y = \bar{A}$$

$$Y = \neg A$$

$$Y = \text{NOT } A$$

## (4) Schaltzeichen eines NICHT-Gatters:

Invertierungskreis auch am Eingang möglich

- Basisfunktionen

- Nützliche Konzepte

- UND, ODER, NICHT Verknüpfungen

- Schaltnetzanalyse

- Zusammengesetzte Gatter

- Schaltungen aus Grundgattern

- Zusammenfassung

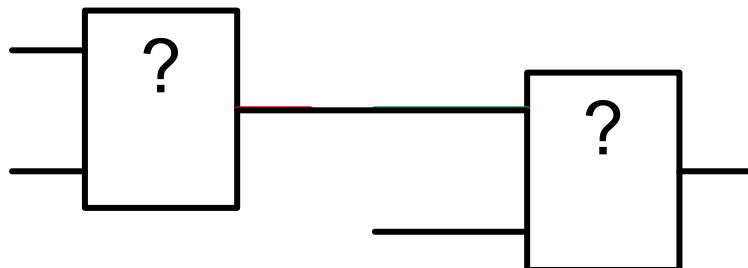

# Wie kann man weitere Schaltfunktionen erhalten?

Mit den **UND**, **ODER**, **NICHT** Grundfunktionen lassen sich alle möglichen Verknüpfungen realisieren.

Dafür müssen diese Grundfunktionen kombiniert werden:

⇒ **Zusammengesetzte Gatter**

Wie bringt man verschiedene Gatter zusammen?

Gatter Aus- und

Eingänge müssen

gekoppelt werden

**So-genannte Schaltnetze resultieren aus dieser Operation**

Die am häufigsten benutzten Gatter, die aus Grundgattern aufgebaut sind, haben ihr eigenes Symbol und Schaltzeichen

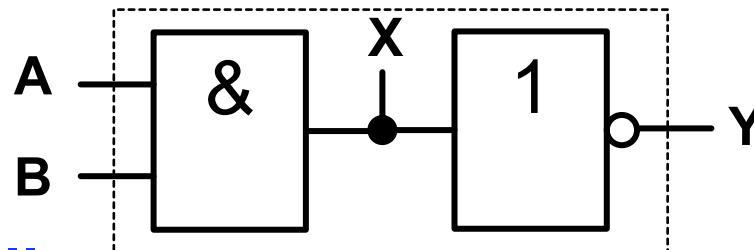

# NAND-Verknüpfung, NAND-Gatter (1)

Invertierung der UND-Funktion

NAND Gatter aus

einem UND und

einem Inverter

## (1) Wahrheitstabelle:

| A | B | X | Y |

|---|---|---|---|

| 0 | 0 | 0 | 1 |

| 0 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 0 |

Nur wenn beide

Eingänge auf 1 liegen,

ist der Ausgang 0

## (2) Schalterlogik:

# NAND-Verknüpfung, NAND-Gatter (2)

## (3) Logische Gleichung der NAND-Verknüpfung:

$$Y = \overline{A \wedge B}$$

$$Y = \overline{A \cdot B}$$

Hier verwendet

$$Y = \overline{A * B}$$

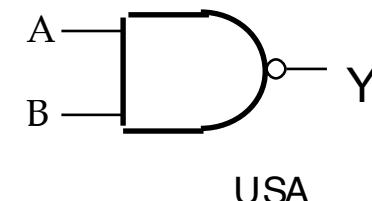

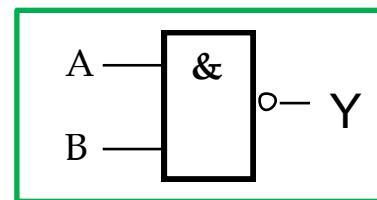

## (4) Schaltzeichen eines NAND-Gatters mit 2 Eingängen:

Hier verwendet

## (5) Zeitverhalten eines NAND-Gatters:

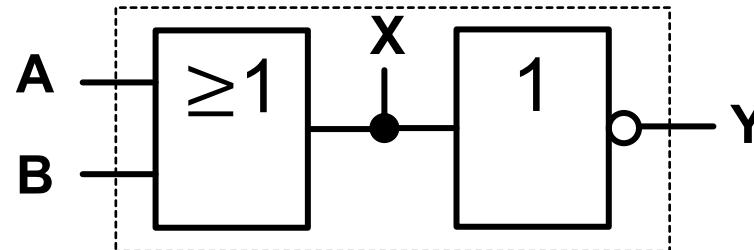

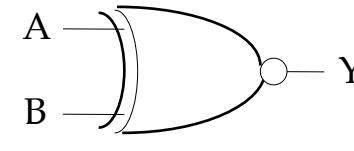

# NOR-Verknüpfung, NOR-Gatter (1)

Invertierung der OR-Funktion

NOR Gatter aus einem OR und einem Inverter

## (1) Wahrheitstabelle:

| A | B | X | Y |

|---|---|---|---|

| 0 | 0 | 0 | 1 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 1 | 0 |

Nur wenn beide Eingänge auf 0 liegen, ist der Ausgang 1

## (2) Schalterlogik:

# NOR-Verknüpfung, NOR-Gatter (2)

## (3) Logische Gleichung der NOR-Verknüpfung:

$$Y = \overline{A \vee B}$$

$$Y = \overline{A + B}$$

## (4) Schaltzeichen eines NOR-Gatters mit 2 Eingängen:

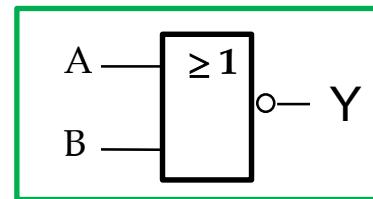

Hier verwendet

## (5) Zeitverhalten eines NOR-Gatters:

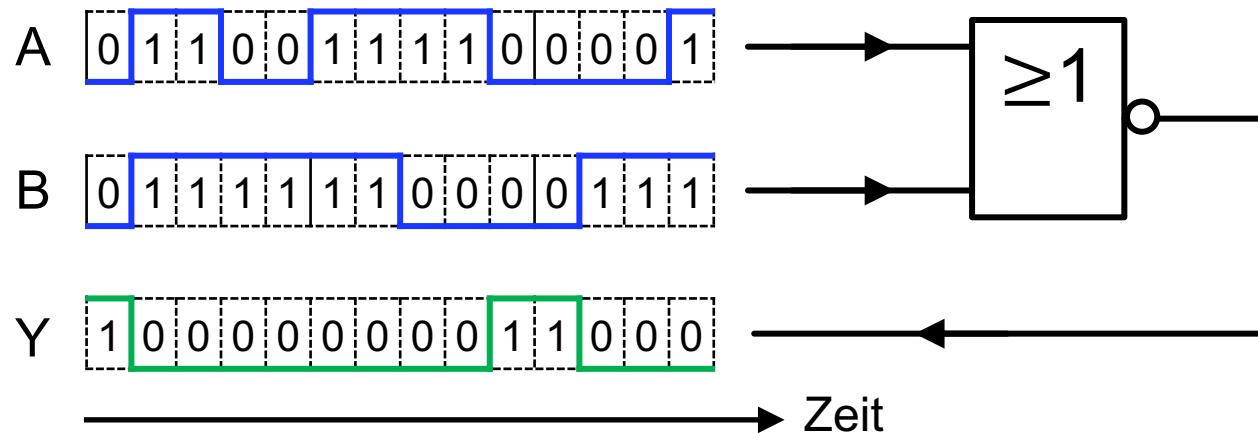

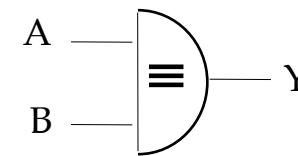

# ÄQUIVALENZ-Verknüpfung, XNOR-GATTER (1)

**Entwurfsziel:** es ist ein Schaltnetz aufzubauen, das eine logische 1 liefert, wenn beide Eingänge gleich sind, sonst 0.

## (1) Schaltnetz:

$$Y = (A \wedge B) \vee (\bar{A} \wedge \bar{B}) = (A \cdot B) + (\bar{A} \cdot \bar{B})$$

# ÄQUIVALENZ-Verknüpfung, XNOR-GATTER (2)

## (2) Wahrheitstabelle: (zu vervollständigen)

| A | B | $S = \bar{A} \wedge \bar{B}$ | $Q = A \wedge B$ | $Y = S \vee Q$ |

|---|---|------------------------------|------------------|----------------|

| 0 | 0 |                              |                  |                |

| 0 | 1 |                              |                  |                |

| 1 | 0 |                              |                  |                |

| 1 | 1 |                              |                  |                |

## (3) Logische Gleichung der XNOR-Verknüpfung:

Hier verwendet

$$Y = \overline{A \oplus B}$$

$$Y = A \leftrightarrow B$$

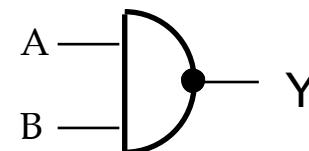

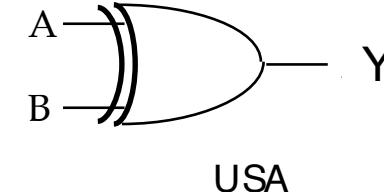

## (4) Schaltzeichen eines XNOR-Gatters mit 2 Eingängen:

Hier verwendet

USA

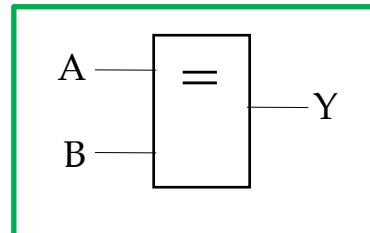

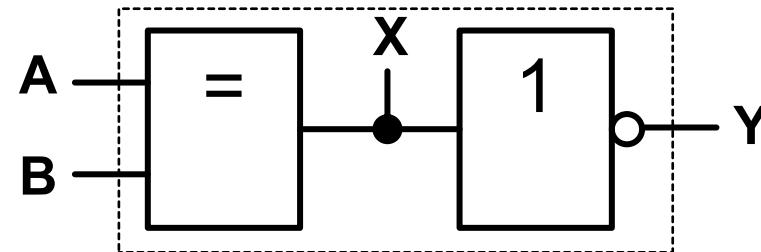

# ANTIVALENZ-Verknüpfung, XOR-Gatter (1)

**Entwurfsziel:** es ist ein Schaltnetz aufzubauen, das eine logische 1 liefert, wenn beide Eingänge ungleich sind, sonst 0.

(Antivalenz = Ungleichwertigkeit)

## (1) Schaltnetz:

XOR Gatter aus

einem XNOR und

einem Inverter

## (2) Wahrheitstabelle:

| A | B | X | Y |

|---|---|---|---|

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 0 |

Nur wenn beide

Eingänge ungleich

sind, ist der Ausgang 1

# ANTIVALENZ-Verknüpfung, XOR-Gatter (2)

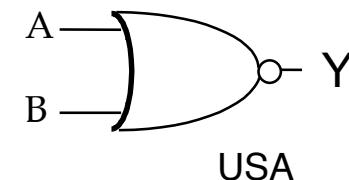

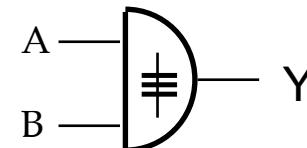

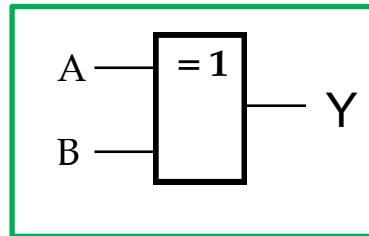

## (3) Logische Gleichung der XOR-Verknüpfung:

Hier verwendet

$$Y = A \oplus B$$

$$Y = A \leftrightarrow B$$

## (4) Schaltzeichen eines XOR-Gatters mit 2 Eingängen:

Hier verwendet

USA

## Bemerkungen:

- Das XOR-Gatter wird auch EXCLUSIV-OR Gatter genannt

- Damit sind wir durch alle existierenden Grundgatter gegangen (AND, OR, NICHT, NAND, NOR, XNOR und XOR)

- Es existieren aber weitere Verknüpfungsmöglichkeiten bei Gattern mit zwei Eingängen

- Basisfunktionen

- Nützliche Konzepte

- UND, ODER, NICHT Verknüpfungen

- Schaltnetzanalyse

- Zusammengesetzte Gatter

- Schaltungen aus Grundgattern**

- Zusammenfassung

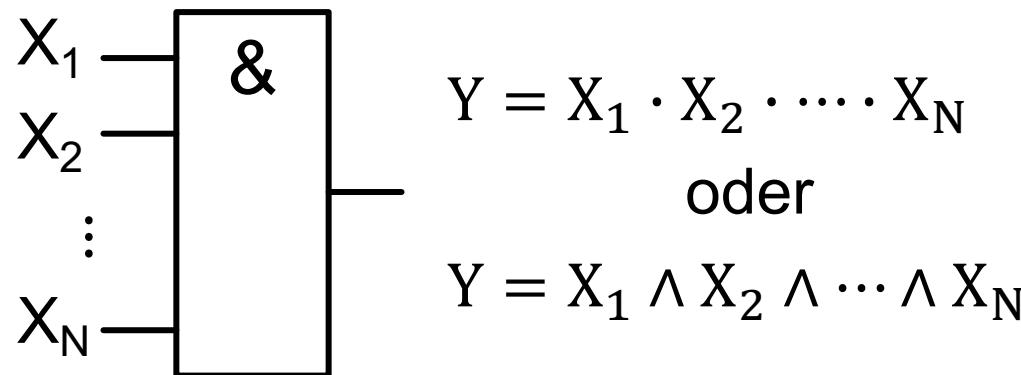

# Grundgatter mit mehreren Eingängen (1)

Die Grundfunktionen sind nicht auf **2** Eingangsvariablen beschränkt, sondern verallgemeinerbar auf **N** Eingängen

## Beispiel 1: UND-Funktion mit N Eingangsvariablen

Wenn alle Eingänge  **$X_1$**  bis  **$X_N$**  den Wert 1 haben, nur dann ist der Ausgang Y ebenfalls 1, sonst 0.

**Frage:** Wie gross ist die Wahrheitstabelle eines UND-Gatters mit 3 Eingängen A, B und C? Vervollständigen Sie die Tabelle auf der nächsten Seite!

# Wahrheitstabelle eines UND-Gatters mit 3 Eingängen

| A | B | C | Y |

|---|---|---|---|

| 0 | 0 | 0 |   |

| 0 | 0 | 1 |   |

| 0 | 1 | 0 |   |

| 0 | 1 | 1 |   |

| 1 | 0 | 0 |   |

| 1 | 0 | 1 |   |

| 1 | 1 | 0 |   |

| 1 | 1 | 1 |   |

## Grundgatter mit mehreren Eingängen (2)

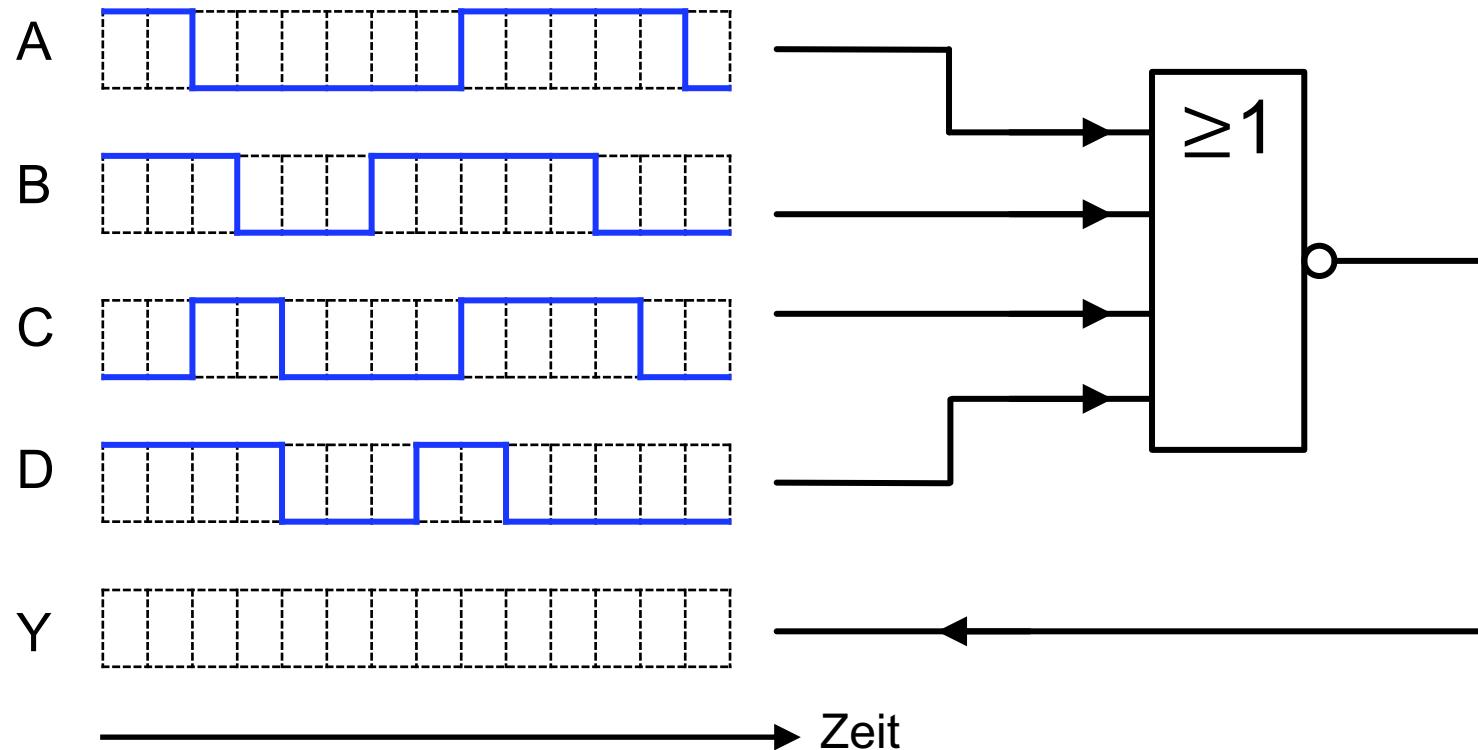

**Beispiel 2:** Die 4 zeitabhängige Eingänge eines NOR-Gatters

A, B, C und D sind unten gegeben:

**Frage:** Wie sieht der zeitabhängige Ausgang Y aus?

# Realisierung von Grundgattern mit mehreren Eingängen

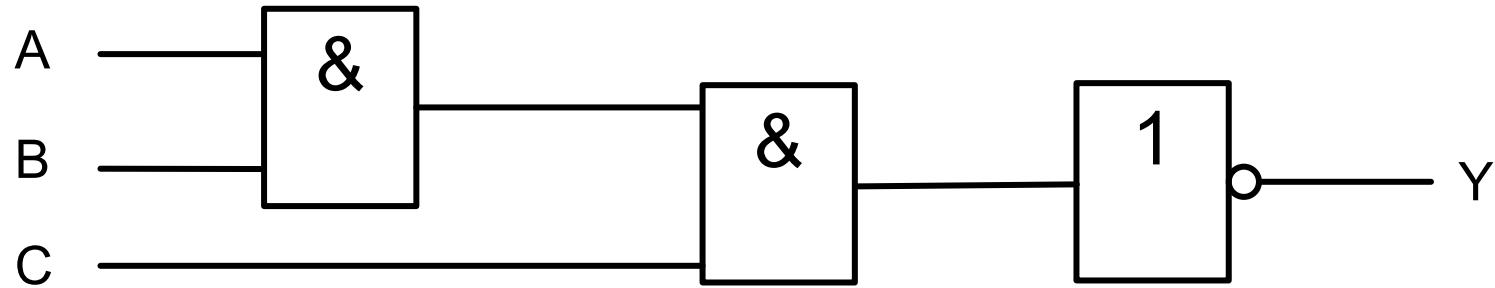

**Beispiel 3:** Ein NAND-Gatter mit 3 Eingängen A, B und C kann durch die Kombination von 3 Grundgattern mit 1-2 Eingängen realisiert werden

Um dieses **Schaltnetz** zu realisieren, sind 5 Schalter erforderlich: 2 für das erste AND-Gatter (Slide 11), 2 für das zweite AND-Gatter (Slide 11) und 1 für das NICHT-Gatter (Slide 19).

**Frage:** Wie kann man ein NAND-Gatter mit 3 Eingängen mit nur 3 Schaltern realisieren? Was wären die Vorteile?

# Realisierung von Grundgattern mit mehreren Eingängen

**Frage:** Wie kann man ein NAND-Gatter mit 3 Eingängen mit nur 3 Schaltern realisieren? Was wären die Vorteile?

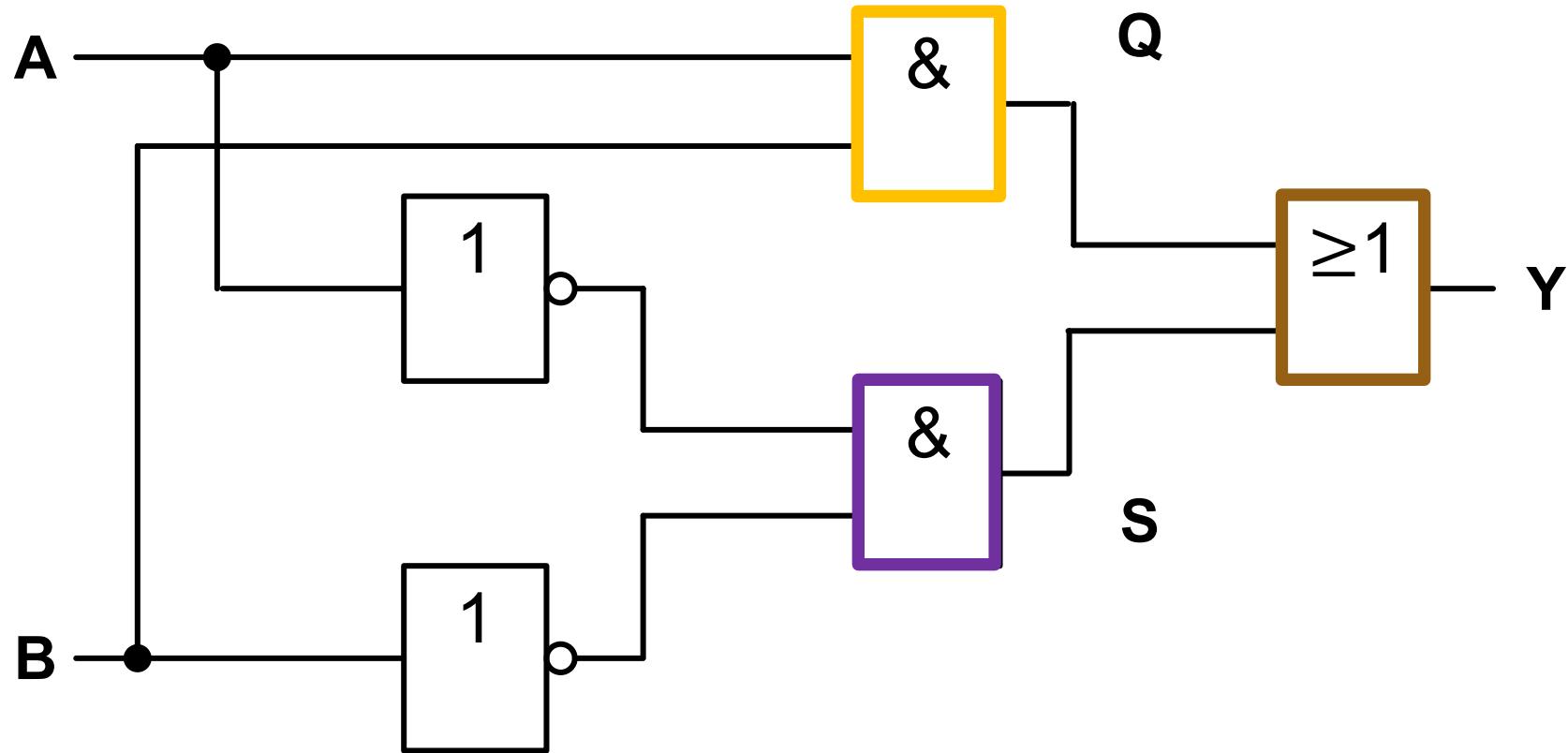

# Schaltnetz zu analysieren

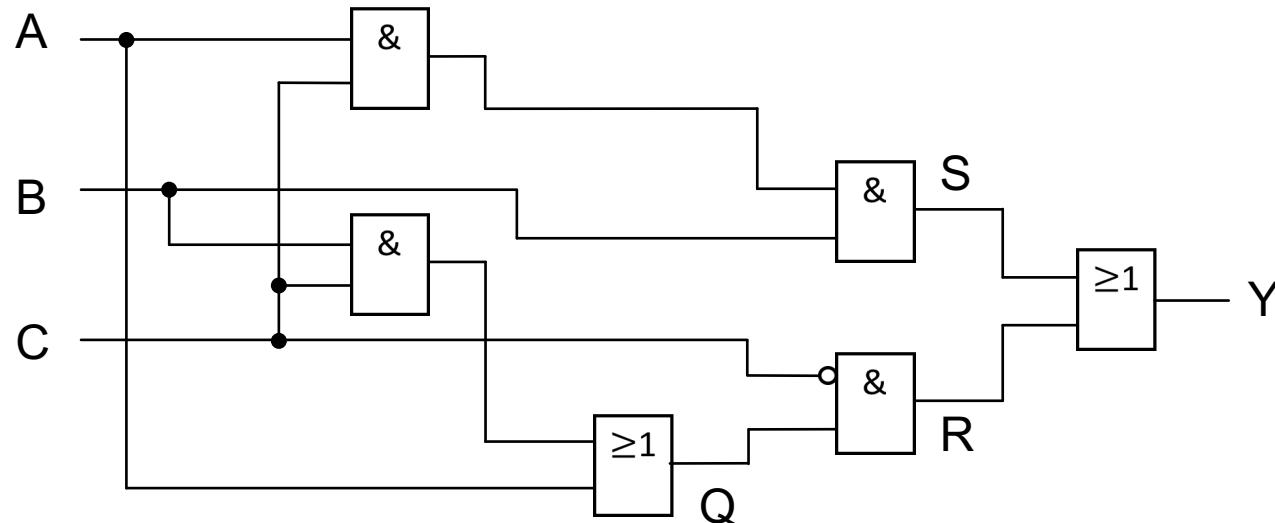

**Beispiel 4:** Das folgende Schaltnetz wurde entworfen. Es besteht aus 3 Eingängen und einem Ausgang

## Fragen:

- Was ist die logische Gleichung für den Ausgang Y?

- Wie sieht die **Wahrheitstabelle** von diesem Schaltnetz aus?

- (Unter welchen Bedingungen ist Y=1?)

$$Y =$$

# Wahrheitstabelle des vorherigen Schaltnetzes

| A | B | C | S | Q | R | Y |

|---|---|---|---|---|---|---|

| 0 | 0 | 0 |   |   |   |   |

| 0 | 0 | 1 |   |   |   |   |

| 0 | 1 | 0 |   |   |   |   |

| 0 | 1 | 1 |   |   |   |   |

| 1 | 0 | 0 |   |   |   |   |

| 1 | 0 | 1 |   |   |   |   |

| 1 | 1 | 0 |   |   |   |   |

| 1 | 1 | 1 |   |   |   |   |

# Bedingungen für Y=1

- Basisfunktionen

- Nützliche Konzepte

- UND, ODER, NICHT Verknüpfungen

- Schaltnetzaanalyse

- Zusammengesetzte Gatter

- Schaltungen aus Grundgattern

- Zusammenfassung

# Zusammenfassung

- Logische Verknüpfungen (UND, ODER, NICHT)

- Wahrheitstabellen mit N Variablen

- Gatter Realisierung durch logische Schalter

- Zusammengesetzte Gatter mit 2 Eingängen

- Gatter mit mehreren Eingängen

- Analyse von komplexen Schaltnetzen

- **Nächste Woche:** CMOS Schaltungen